|

contact us

Tel: (65) 63742113 Operation Hours

Monday to Friday |

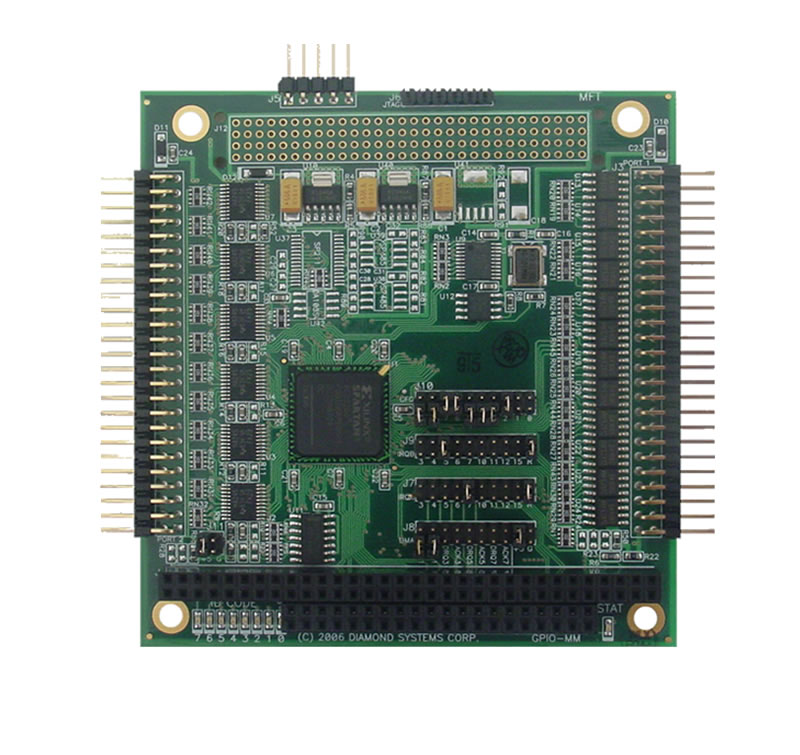

GPIO-MM-21-XT

PC/104 96-ch. Digital I/O

- Description

- Specifications

- Ordering Guide

GPIO-MM-21 is part of a family of reconfigurable digital I/O and counter / timer modules with various port and pin configurations. Each board uses identical hardware with a 200K gate Xilinx Spartan II RAM-based FPGA. The varying configurations are based on different FPGA code. The FPGA code is stored in a flash memory on the board, enabling GPIO-MM-21 to be reprogrammed in the field with different designs, including custom designs.

The GPIO-MM-21 configuration provides 96 digital I/O lines. 48 lines are buffered. The 96 digital I/O lines are compatible with our legacy GMM and OMM boards. This configuration combines the features of two 48-line digital I/O boards into one board to reduce your PC/104 stack size and cost.

Other GPIO-MM configurations provide 48 digital I/O lines with 10 16-bit counter/timers i.e. GPIO-MM-XT.

| Base FPGA | Xilinx Spartan II, 200,000 gates, 40K RAM bits |

| Input Clock | 40MHz |

| FPGA Code Storage | Flash memory, field upgradeable via JTAG |

| ID Indicator | 8-bit LED display indicates FPGA code personality |

| No. of I/O pins | 100 pins (48 buffered) |

| Programmable Digital I/O | 96 programmable, 48 buffered & 48 unbuffered |

| Output Current, Buffered I/O | Logic 0: 64mA max per line |

| Dimensions | 90 x 96 mm |

| Power Supply | +5VDC ±5% |

| Operating Temperature | -40 to +85°C |

| Model | Description |

| GPIO-MM-21-XT | PC/104 96-ch. DIO |