|

contact us

Tel: (65) 63742113 Operation Hours

Monday to Friday |

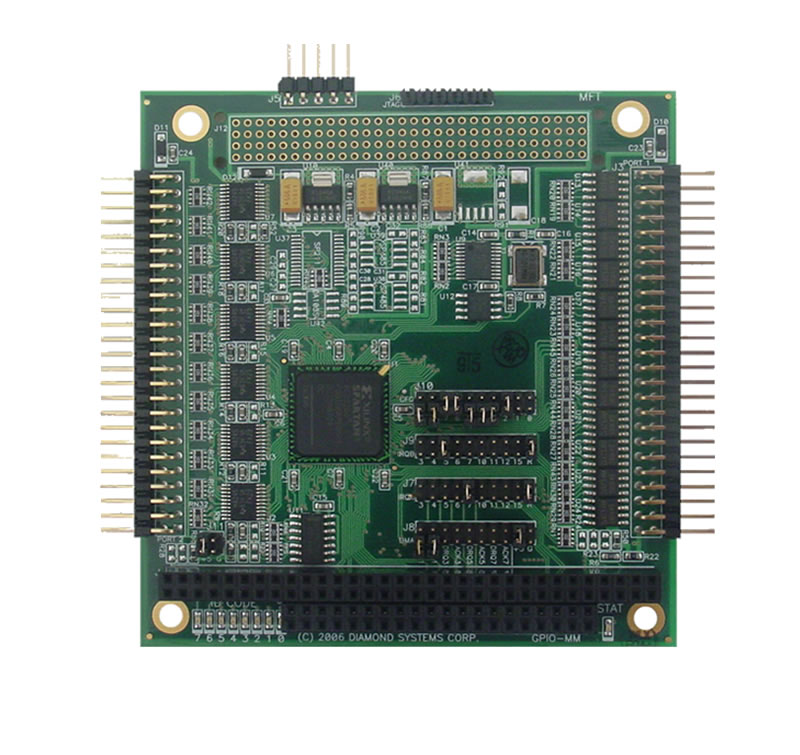

GPIO-MM-XT

PC/104 48-ch DIO with 10 Counter/Timers

- Description

- Specifications

- Ordering Guide

GPIO-MM is a FPGA-based digital I/O module, allowing multiple feature sets to be implemented on the same hardware platform. The FPGA is a Xilinx Spartan 2 RAM-based device with 200K gates (XC2S200). An on-board configuration flash memory device stores the FPGA code for automatic loading on power-up, and new code can be downloaded using a JTAG cable connected to a PC. Several standard off the shelf personalities are available, and custom ones can be developed either by users with Xilinx tools or by Diamond as a customization service.

| Base FPGA | Xilinx Spartan II, 200,000 gates, 40K RAM bits |

| Input Clock | 40MHz |

| FPGA Code Storage | Flash memory, field upgradeable via JTAG |

| ID Indicator | 8-bit LED display indicates FPGA code personality |

| No. of I/O pins | 100 pins (48 buffered) |

| Programmable Digital I/O | 48 using 8255 cores |

| Fixed Direction I/O | 8 fixed inputs and 8 fixed outputs |

| Counter/Timers | 10 16-bit, using 9513 cores |

| Max counting frequency | 40MHz |

| Counter modes | Counter, rate/square-wave generator, pulse-width modulator, programmable one-shot, hardware/software triggered strobe |

| Output Current, Buffered I/O | Logic 0: 64mA max per line |

| Output Current, Fixed I/O & Fixed Counter/Timers | ±24mA max. |

| Dimensions | 90 x 96 mm |

| PC/104 bus | 16-bit stackthrough ISA bus |

| Power Supply | +5VDC ±5% |

| Operating Temperature | -40 to +85°C |

| Model | Description |

| GPIO-MM-XT | PC/104 48-ch. DIO with 10 Counters/Timers |